引言

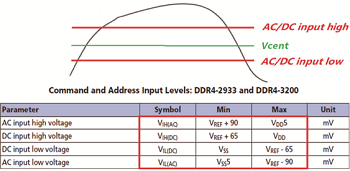

对于业界内两种主要的信号模块:DDR模块和高速串行链路模块,针对信号质量,在仿真评估中都会给出比较明确的时域标准。例如传统DDR4的地址控制信号中,会以高低电平阈值来约束DDR4的信号质量,如图1所示。

图1 DDR4地址控制信号阈值标准

如果从DDR4升级到DDR5,DDR5的地址控制信号质量的判断标准会变成眼图的形式,如图2所示。

图2 DDR5地址控制信号眼图标准

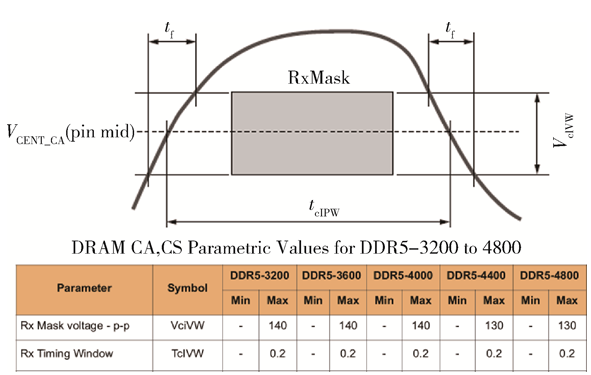

DDR5的眼图判断形式其实就很像传统意义上的高速串行信号了,图3是某芯片的25 Gb/s信号的眼图接收要求。

图3 某芯片25 Gb/s高速串行信号眼图接收标准

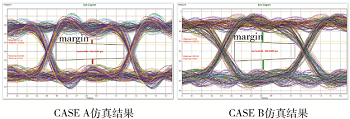

每种不同的信号类型有了对应的判断标准外,不同的工程师在信号质量满足标准后,对裕量的要求可能会不同,图4给出了不同裕量仿真结果对比。大家总是希望有更多的裕量,例如还是上述的DDR4的地址控制信号仿真结果,如图5所示,当两个仿真结果都能满足判断标准之后,相信大家更希望获得case B仿真结果的设计,毕竟它的裕量更大。

图4 DDR4地址控制信号仿真结果裕量对比

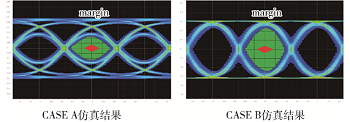

图5 25 Gb/s高速串行信号仿真结果裕量对比

同样在高速串行信号也存在同样的选择,眼图裕量大的case总是大家的第一选择。

不同裕量的仿真结果其实代表着仿真参数的不同,在DDR信号仿真中,可能代表着主控芯片驱动或者颗粒ODT值的不同,对于高速串行信号仿真而言,则可能是芯片的加重均衡参数的不同。那么本节就带出一个值得思考的问题,到底在仿真中如何能够准确且快速地找到最佳的参数从而得到最大裕量的仿真结果呢?

本文详细内容请下载:

http://www.chinaaet.com/resource/share/2000006120

作者信息:

黄刚,吴均

(深圳市一博科技股份有限公司, 广东 深圳 518051)