英特尔展示AI芯片测试平台 8倍光罩尺寸封装设计

发布日期:2026-02-03

来源:芯智讯

1月30日,英特尔展示了一款名为“AI芯片测试平台”的先进技术,这款原型系统采用了8倍光罩尺寸的封装设计,内含 4 个逻辑芯片、12 个HBM4 高带宽内存堆叠及两个I/O芯片。这个展示不仅突显英特尔在人工智智能(AI)和高性能计算(HPC)应用领域的最新封装能力,还显示出其在多芯片设计方面的潜力。

英特尔的这款测试平台并不是一个运行中的AI加速器,而是一个展示未来AI和HPC处理器如何实际组装的工具。该平台的核心是基于Intel 18A制程技术的四个大型逻辑芯片,这些芯片周围环绕着HBM4高带宽内存和I/O芯片,并通过EMIB-T 2.5D桥接技术相连。这种设计不仅提高了互连密度,还优化了电力传输。

此外,英特尔的测试平台还预示着其向垂直整合的迈进。公司计划开发专为芯片堆叠设计的Intel 18A-PT制程技术,这将使得逻辑芯片或内存能在垂直方向上进行堆叠,并且能够实现更高效的电力供应。

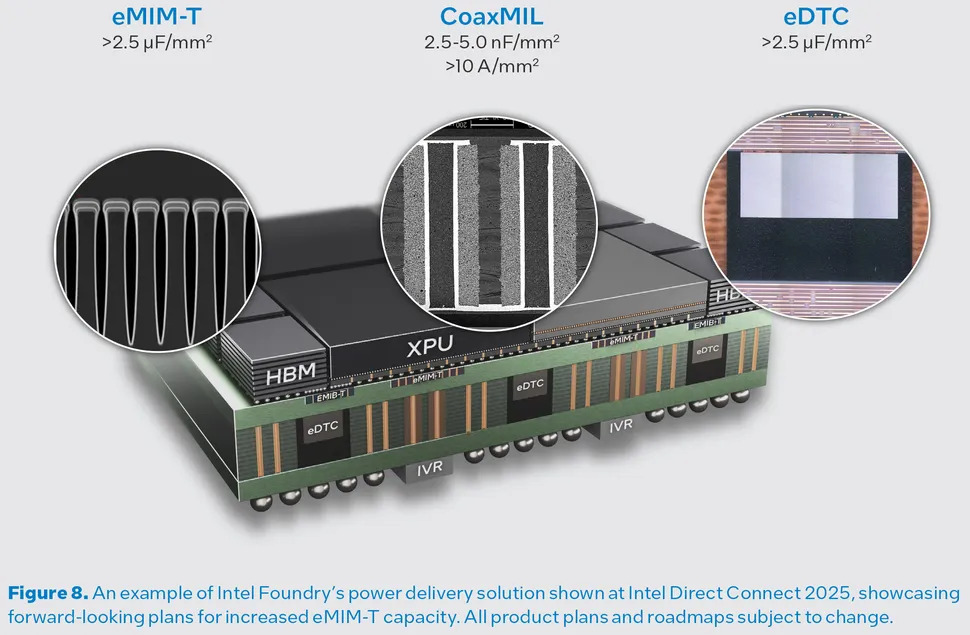

在多芯片AI和HPC加速器的设计中,电力供应是主要的设计约束。英特尔的这个平台结合最新的电力相关创新,旨在支持快速的电流波动,满足生成式AI工作负载的需求。

尽管英特尔的“AI芯片测试平台”展示了其在技术上的进步,但未来是否会有基于此架构的量产产品仍然有待观察。英特尔计划在2027年推出代号为Jaguar Shores的AI加速器,是否会采用目前展示的架构尚不明朗。